- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

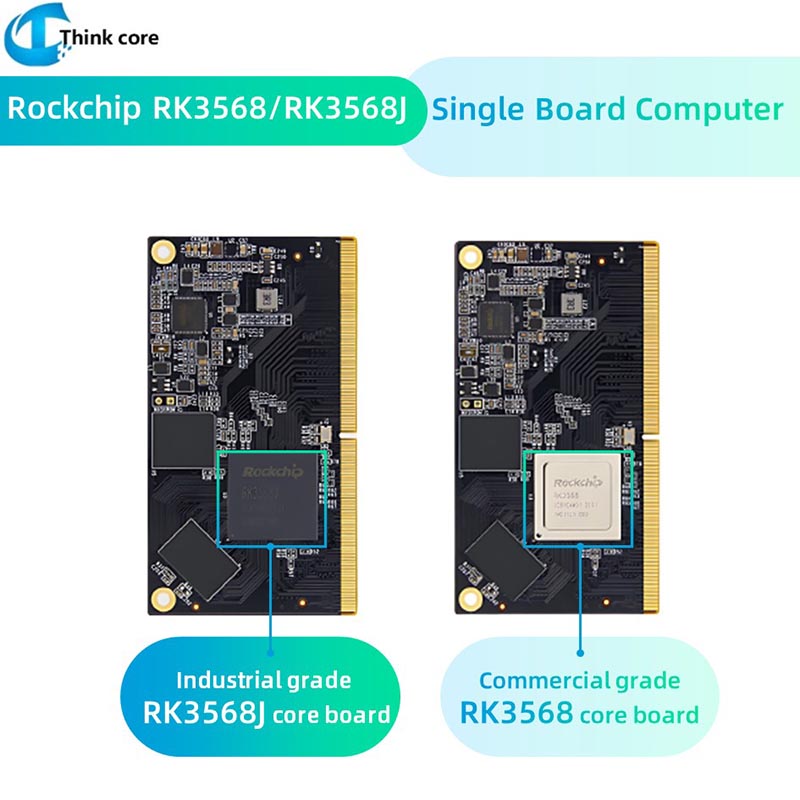

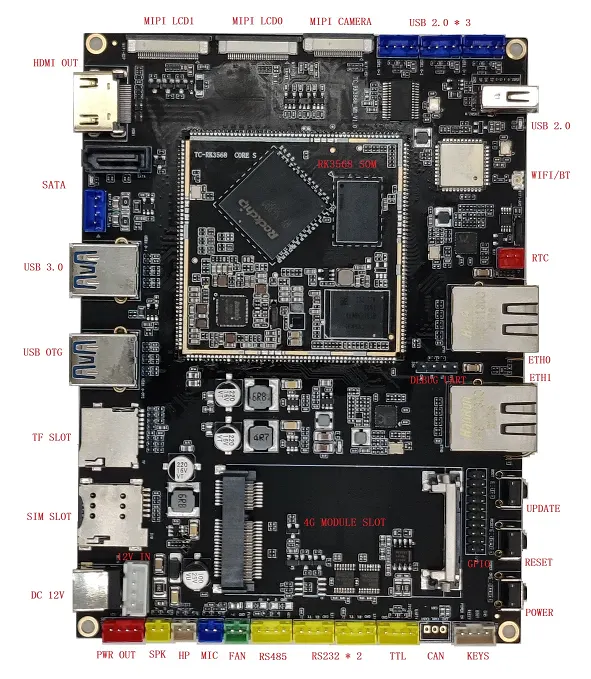

Scheda centrale RK3568

RK3568, il processore Cortex-A55 quad-core a 64 bit, con processo di litografia a 22 nm, ha una frequenza fino a 2,0 GHz, offrendo prestazioni efficienti e stabili per l'elaborazione dei dati delle apparecchiature di back-end. Ci sono una varietà di opzioni di archiviazione, consentendo ai clienti di implementare rapidamente la ricerca e la produzione di prodotti. Supporta fino a 8 GB di RAM, con larghezza fino a 32 bit e frequenza fino a 1600 MHz. Supporta l'ECC all-data-link, rendendo i dati più sicuri e affidabili e soddisfacendo i requisiti per l'esecuzione di applicazioni con prodotti di memoria di grandi dimensioni. È integrato con GPU dual-core, VPU ad alte prestazioni e NPU ad alta efficienza. La GPU supporta OpenGL ES3.2/2.0/1.1, Vulkan1.1. La VPU può raggiungere la decodifica video 4K 60fps H.265/H.264/VP9 e la codifica video 1080P 100fps H.265/H.264. L'NPU supporta la commutazione con un clic di framework tradizionali come Caffe/TensorFlow.

Invia richiesta PDF Scarica

Thinkcore TC-RK3568 Specifica della scheda di sviluppo del foro del timbro

Dichiarazione sul diritto d'autore

I diritti d'autore di questo manuale appartengono a Shenzhen Thinkcore Technology Co., Ltd. e tutti i diritti sono riservati. Non è consentito a società o privati estrarre parte o tutto il presente manuale, i trasgressori saranno perseguiti a norma di legge.

Attenzione:

I manuali della piattaforma di sviluppo in vendita verranno aggiornati di volta in volta, si prega di scaricare l'ultimo manuale dal sito Web www.think-core.com o contattare il nostro rappresentante di vendita dell'azienda, non ci sarebbero ulteriori avvisi.

Nota di rilascio

|

Versione |

Data |

Autore |

Descrizione |

|

Rev.01 |

2022-08-04 |

|

Revisione |

Capitolo 1. Introduzione alla scheda di sviluppo del foro del timbro TC-RK3568

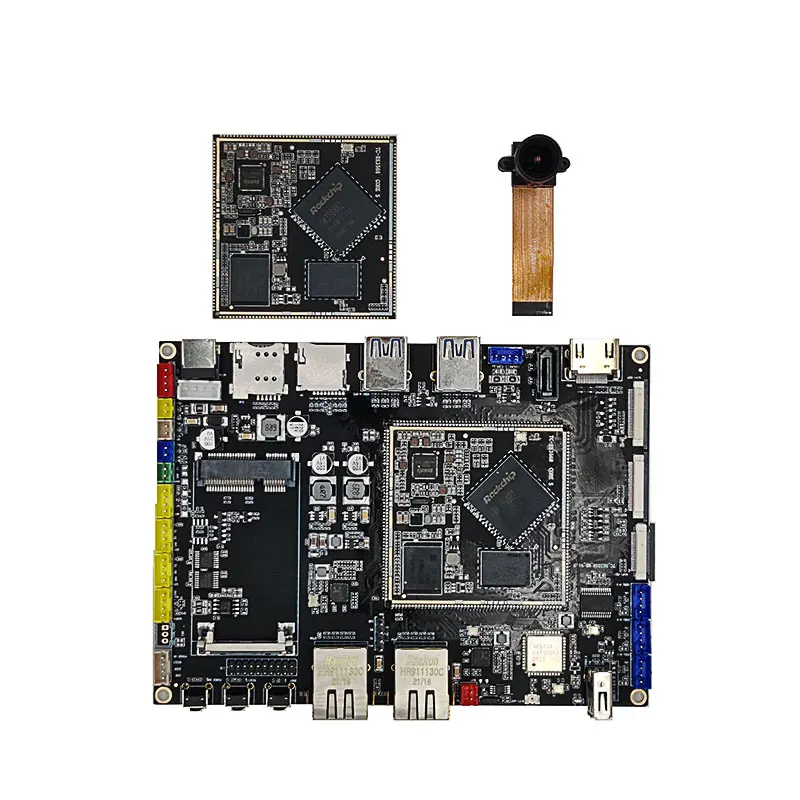

TC-RK3568 Riassunto della scheda di sviluppo del foro del timbro

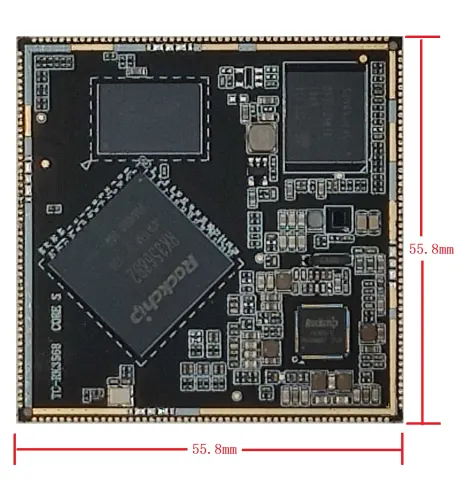

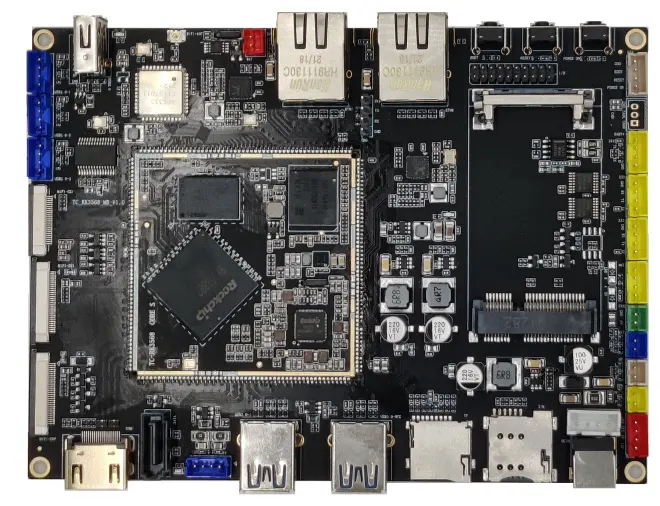

TC-RK3568 Stamp Hole Development Board include TC-RK3568 Stamp Hole SOM e carrier baord.

Il sistema Stamp Hole TC-RK3568 sul modulo è dotato di processore Rockchip a 64 bit RK3568 configurato con GPU dual-core e NPU ad alte prestazioni.

RK3568, il processore Cortex-A55 quad-core a 64 bit, con processo di litografia a 22 nm, ha una frequenza fino a 2,0 GHz, offrendo prestazioni efficienti e stabili per l'elaborazione dei dati delle apparecchiature di back-end. Ci sono una varietà di opzioni di archiviazione, consentendo ai clienti di implementare rapidamente la ricerca e la produzione di prodotti. Supporta fino a 8 GB di RAM, con larghezza fino a 32 bit e frequenza fino a 1600 MHz. Supporta l'ECC all-data-link, rendendo i dati più sicuri e affidabili e soddisfacendo i requisiti per l'esecuzione di applicazioni con prodotti di memoria di grandi dimensioni. È integrato con GPU dual-core, VPU ad alte prestazioni e NPU ad alta efficienza. La GPU supporta OpenGL ES3.2/2.0/1.1, Vulkan1.1. La VPU può raggiungere la decodifica video 4K 60fps H.265/H.264/VP9 e la codifica video 1080P 100fps H.265/H.264. L'NPU supporta la commutazione con un clic di framework tradizionali come Caffe/TensorFlow.

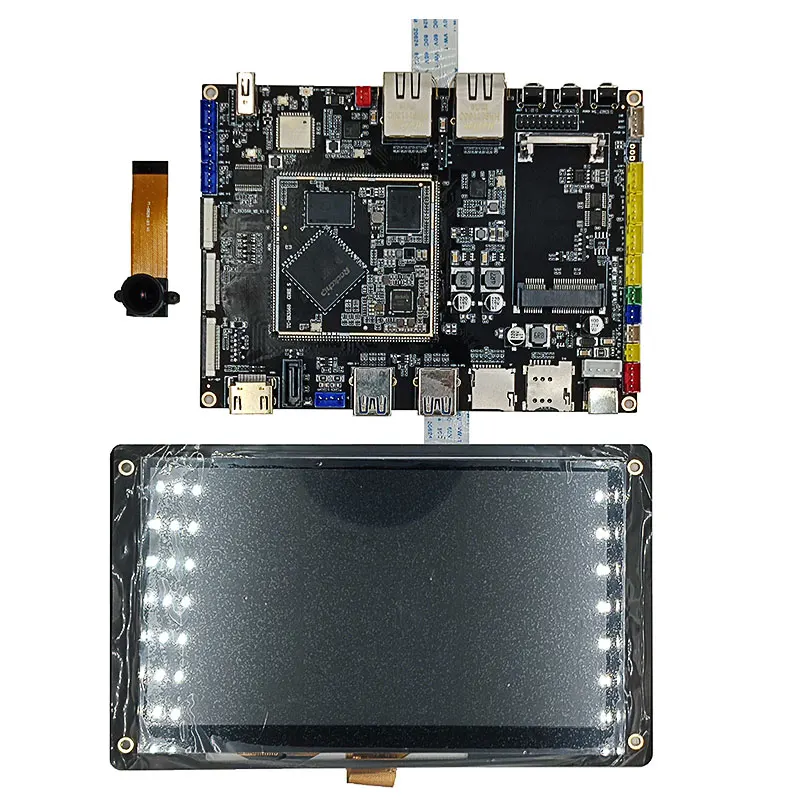

Con MIPI-CSI x2, MIPI-DSI x2, HDMI2.0, interfacce video EDP, può supportare fino a tre uscite schermo con display diverso. L'ISP 8M integrato supporta doppia fotocamera e HDR. L'interfaccia di ingresso video può essere collegata a una telecamera esterna o a più telecamere. È dotato di doppie porte Gigabit Ethernet RJ45 adattive, attraverso le quali è possibile accedere e trasmettere dati di rete interni ed esterni, migliorando l'efficienza della trasmissione di rete e soddisfacendo le esigenze di prodotti con più porte di rete come NVR e gateway industriale.

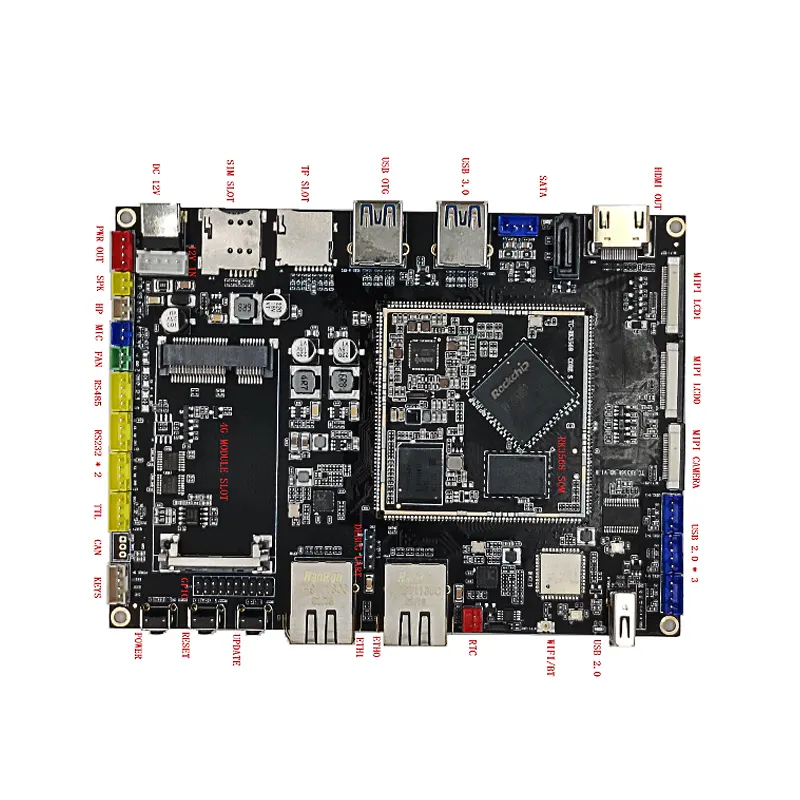

La scheda carrier include molte interfacce, come porta 4G LTE, USB 3.0, USB 2.0, PCIE, doppia Ethernet, WIFI, Bluetooth, ingresso e uscita audio, uscita HDMI, display MIPI DSI, display eDP, display LVDS, MIPI CSI fotocamera, slot per schede TF, RS485, RS232, TTL, CAN, alimentazione, SATA, ecc.

Sono supportati Android 11, sistema operativo Ubuntu 18.04, sistema operativo Debian e Linux Buildroot. Il funzionamento stabile e affidabile fornisce un ambiente di sistema sicuro e stabile per la ricerca e la produzione di prodotti.

Un SDK completo, documenti di sviluppo, esempi, documenti tecnologici, tutorial e altre risorse sono forniti agli utenti per effettuare un'ulteriore personalizzazione.

Caratteristiche della scheda di sviluppo del foro del timbro TC-RK3568:

Dimensioni: 150 mm x 110 mm.

Interfacce ricche, possono essere utilizzate direttamente in vari prodotti intelligenti per facilitare il completamento dei prodotti.

Sono supportati Android 11.0, sistema operativo Ubuntu 18.04, sistema operativo Debian e Linux Buildroot.

Applicazione

Questa scheda può essere ampiamente utilizzata in NVR intelligenti, terminali cloud, gateway IoT, controllo industriale, edge computing, gate di riconoscimento facciale, NAS, console centrali dei veicoli, ecc.

Parametro caratteristico

|

Specifiche |

|

|

processore |

RockChip RK3568, Cortex-A55 quad-core a 64 bit, processo di litografia a 22 nm, frequenza fino a 2,0 GHz |

|

GPU |

BRACCIO G52 2EE Supporta OpenGL ES 1.1/2.0/3.2, OpenCL 2.0, Vulkan 1.1 Hardware di accelerazione 2D ad alte prestazioni integrato |

|

NPU |

0.8Tops@INT8, acceleratore AI ad alte prestazioni integrato RKNN NPU Supporta la commutazione con un clic di Caffe/TensorFlow/TFLite/ONNX/PyTorch/Keras/Darknet |

|

VPU |

Supporta la decodifica video 4K 60fps H.265/H.264/VP9 Supporta la codifica video 1080P 100fps H.265/H.264 Supporta ISP 8M, supporta HDR |

|

RAM |

2GB/4GB/8GB |

|

Conservazione |

eMMC da 8 GB/16 GB/32 GB/64 GB/128 GB Supporta SATA 3.0 x 1 (espandibile con SSD/HDD da 2,5â) Supporta slot per schede TF x1 (espandibile con scheda TF) |

|

Sistema operativo |

Android11/Linux Buildroot/Ubuntu/Debian |

|

Caratteristiche dell'hardware |

|

|

Schermo |

1 * HDMI2.0, supporta l'uscita 4K@60fps 1 * MIPI DSI, supporta l'uscita 1920*1080@60fps 1 * LVDS, supporta l'uscita 1920*1080@60fps 1 * eDP1.3, supporta l'uscita 2560x1600@60fps |

|

Ethernet |

Supporta due porte Gigabit Ethernet (1000 Mbps) |

|

Wi-Fi |

Mini PCIe per collegare 4G LTE Supporta Wi-Fi 6 (802.11AX) Supporta BT5.0 |

|

PCIE3.0 |

Supporta l'interfaccia PCE3.0 |

|

Audio |

1 * Uscita audio HDMI 1 * Uscita altoparlante 1 * Uscita per auricolari 1 * Ingresso audio microfono integrato |

|

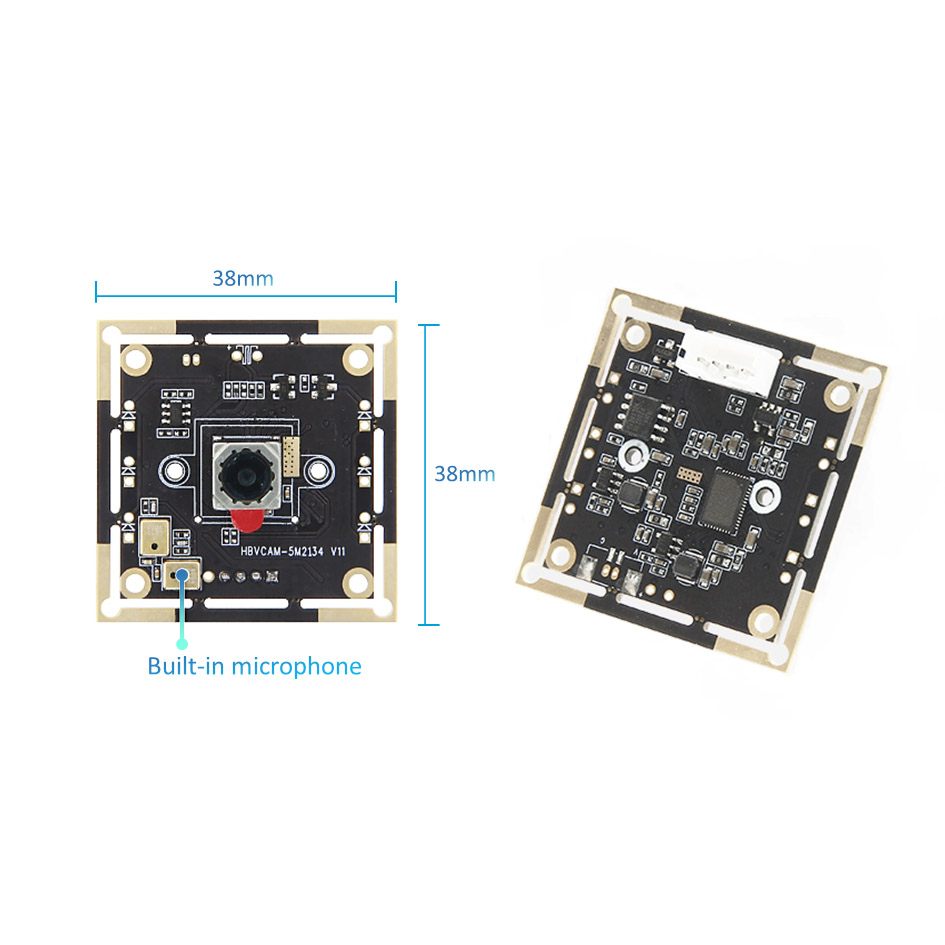

Telecamera |

Supporta l'interfaccia della fotocamera MIPI-CSI a 1 canale Supporta HDR, l'immagine rimane nitida in controluce o in condizioni di luce intensa

|

|

USB |

1 * host USB 3.0, 4 * host USB 2.0, 1 * USB 3.0 OTG |

|

SATA |

1 * SATA, 6,0 Gb/s |

|

Seriale |

1 * TTL, 2 * RS232, 1 * RS485 |

|

POTERE |

Supporto CAN2.0B, supporto 1Mbps, 8Mbps |

|

Carta TF |

1 slot per schede TF |

|

Altri |

GPIO e ADC |

|

Misurare |

150mm*110mm |

|

|

|

|

Tensione di ingresso |

12V/3A |

|

Temperatura di conservazione

|

-30~80℃ |

|

temperatura di esercizio |

-20~60℃ |

|

Umidità di stoccaggio |

10%~80% |

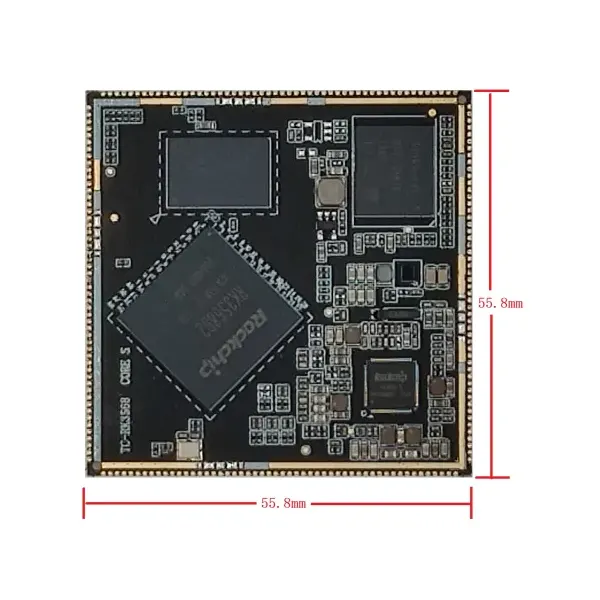

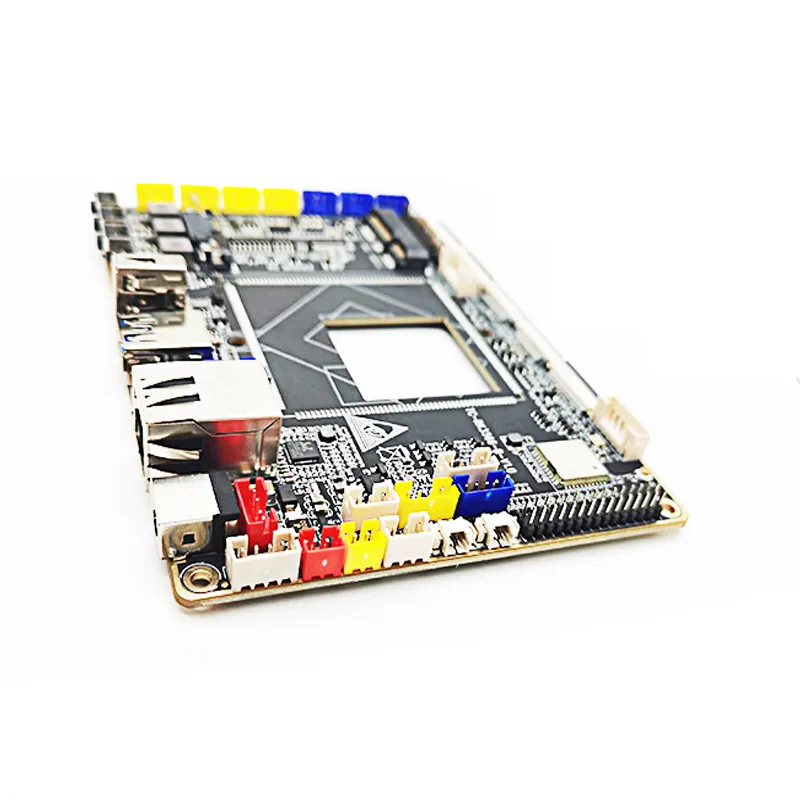

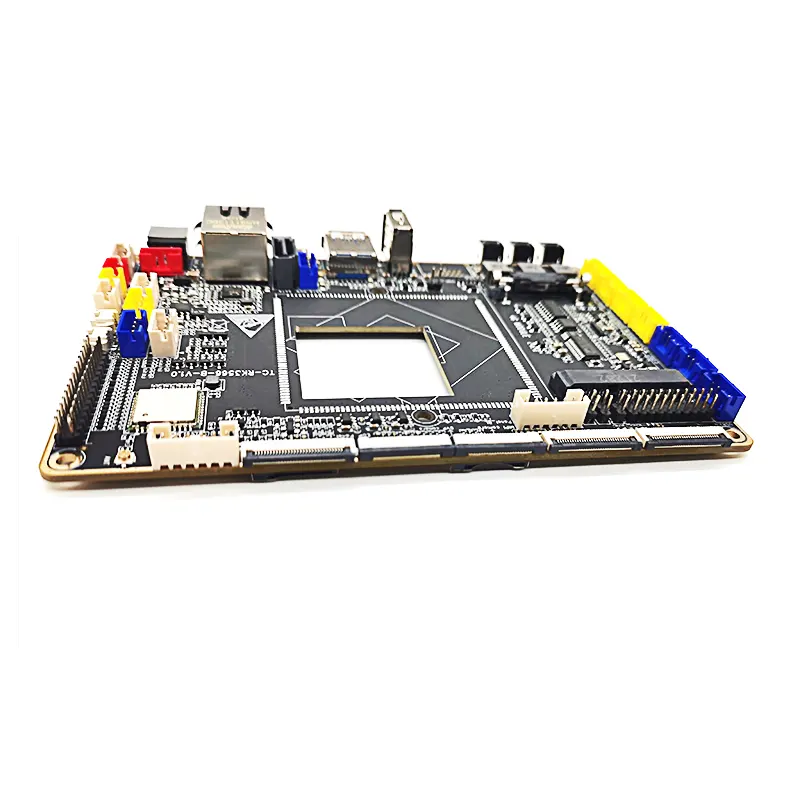

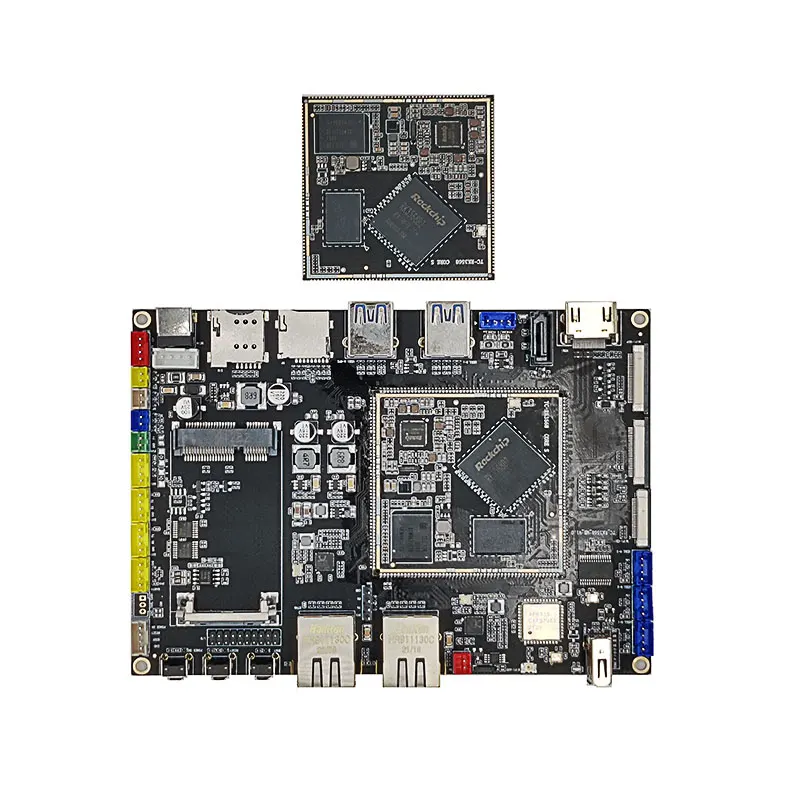

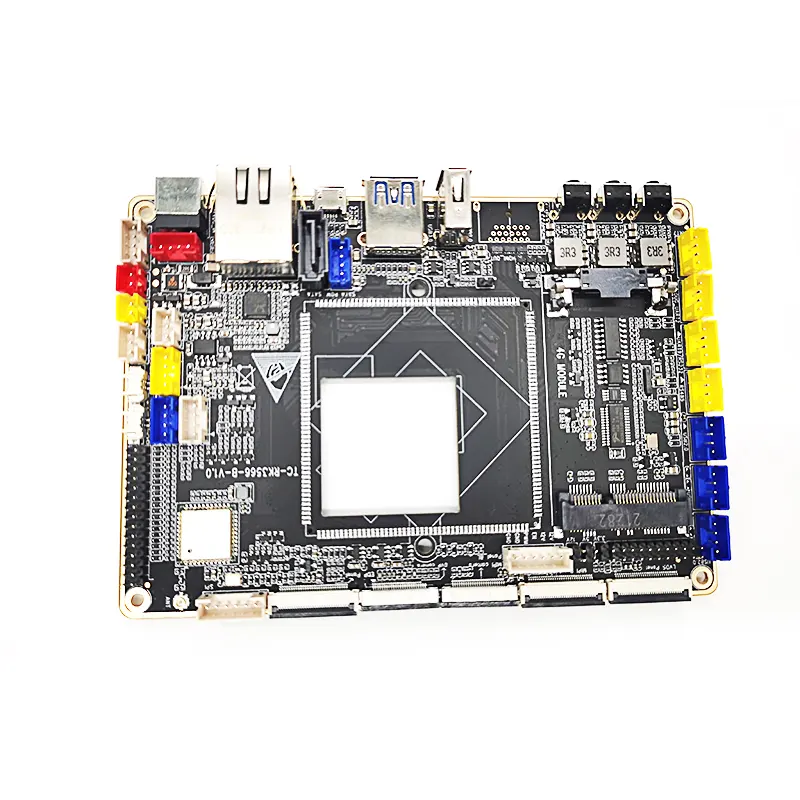

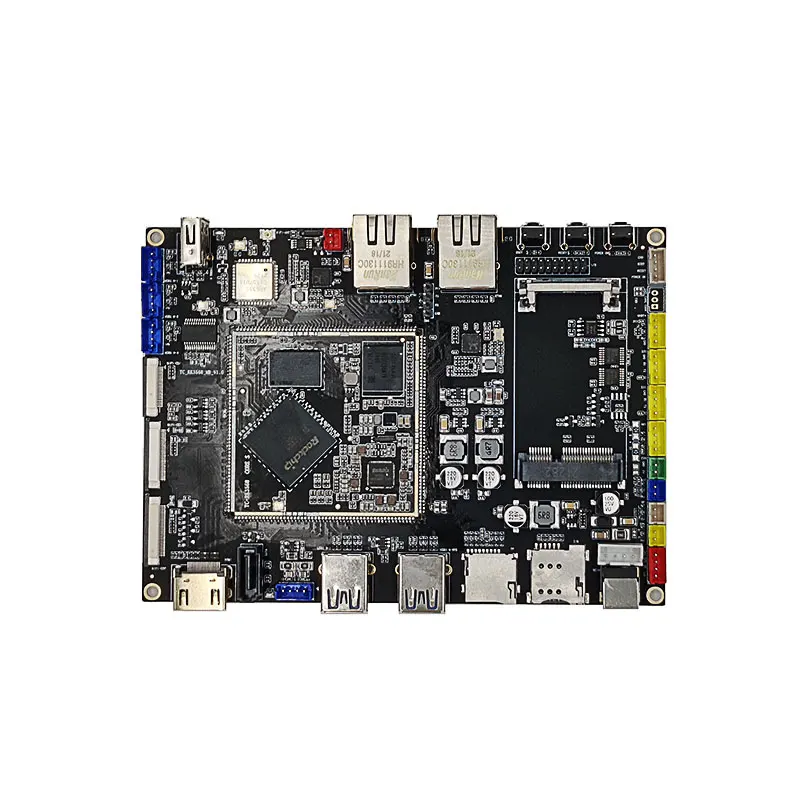

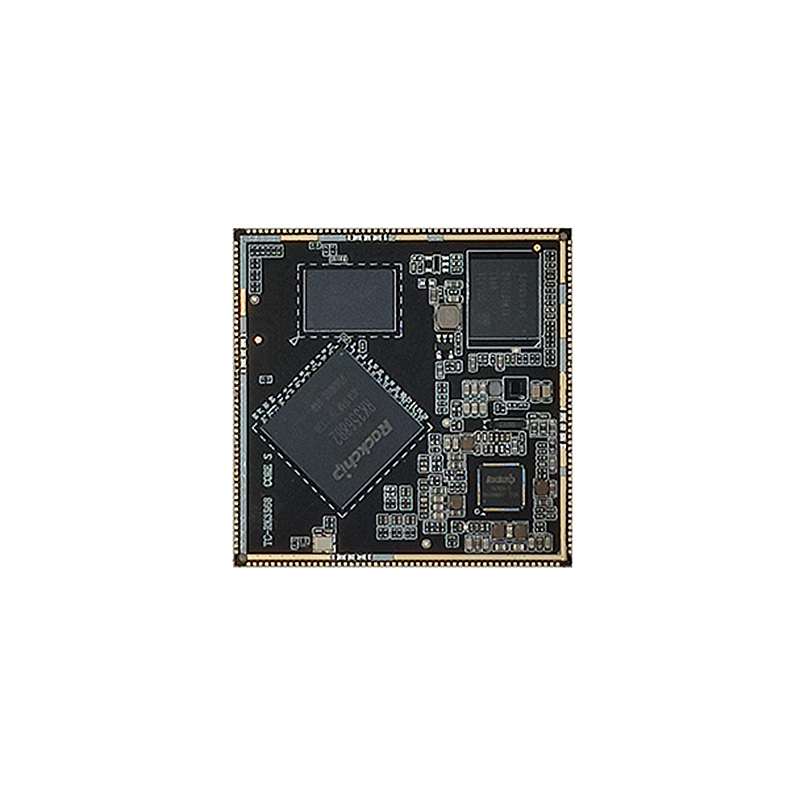

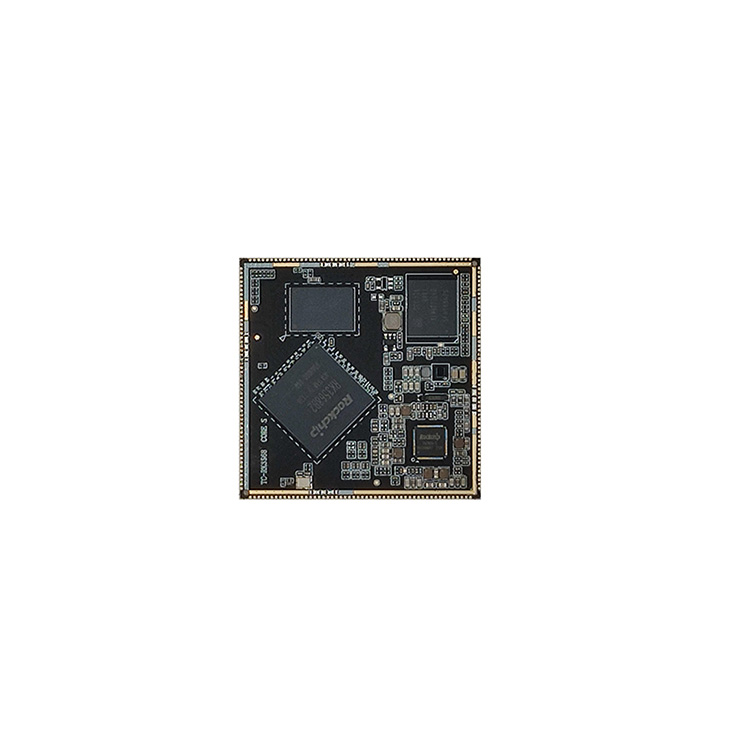

SOM Aspetto

Fronte SOM

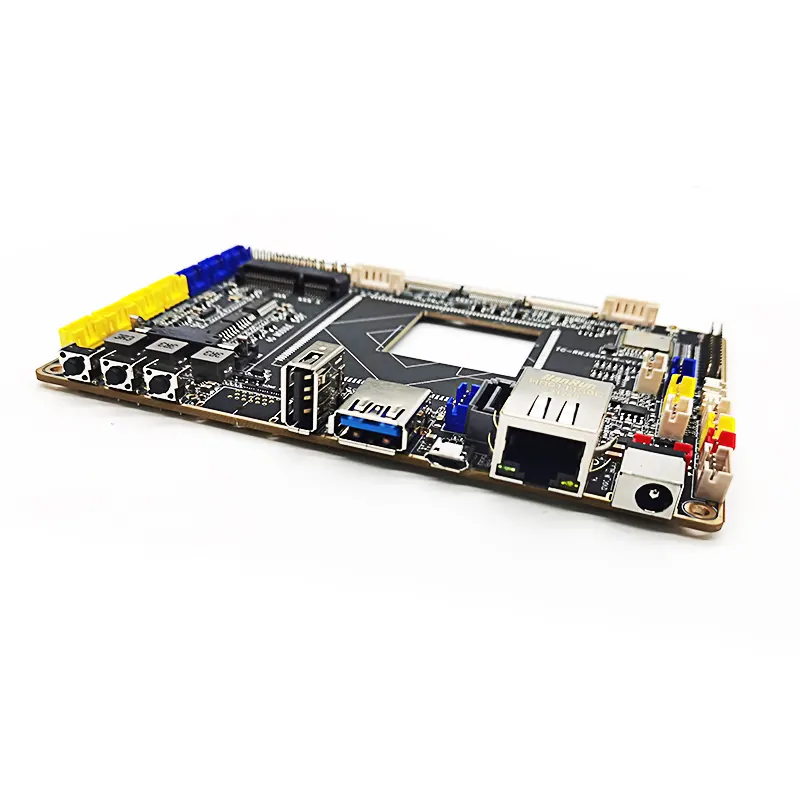

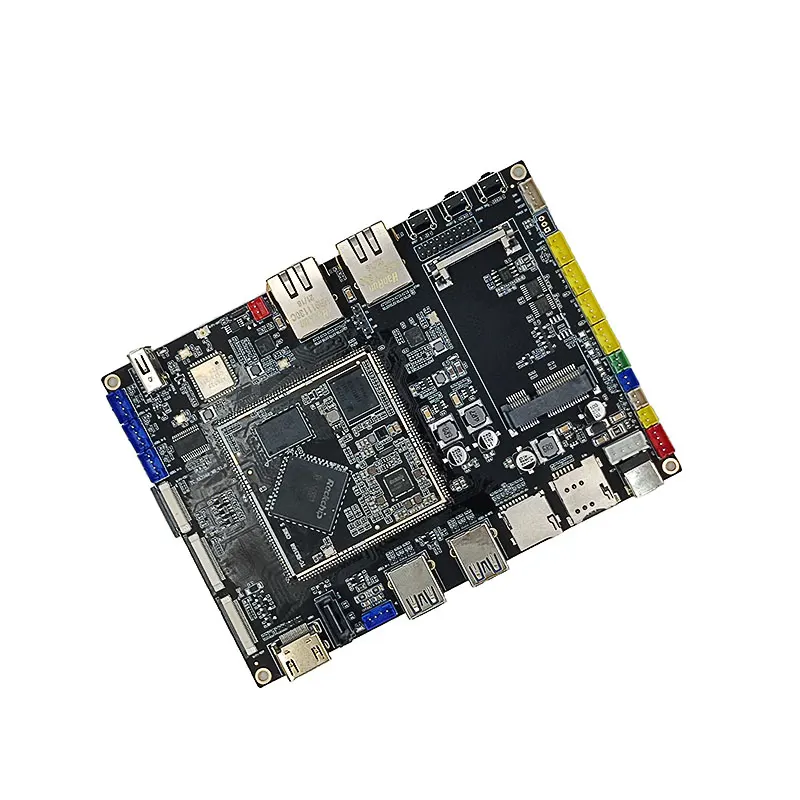

Aspetto della scheda di sviluppo

Capitolo 2. Definizione PIN SOM

PIN SOM Definizione

|

SPILLO |

Definizione dei pin della scheda madre |

Funzione predefinita |

Descrizione della funzione predefinita |

Potere IO |

Tiro IO tipo pad |

|

1 |

VCC3V3_SYS |

Alimentazione del sistema da 3,3 V |

Tensione di ingresso 3,3 V |

|

- |

|

2 |

VCC3V3_SYS |

Alimentazione del sistema da 3,3 V |

Tensione di ingresso 3,3 V |

|

- |

|

3 |

GND |

GND |

GND |

|

- |

|

4 |

GND |

GND |

GND |

|

- |

|

5 |

SDMMC0_DET_L |

SDMMC0_DET/SATA_CP_DET/PCIE30X1_CLKREQn_M0/GPIO0_A4_u |

SDMMC0 rileva ingresso |

3,3 V |

I/O SU |

|

6 |

SDMMC0_D3 |

SDMMC0_D3/ARMJTAG_TMS/UART5_RTSn_M0/GPIO2_A0_u |

Porta dati SDMC0 |

3,3 V |

I/O SU

|

|

7 |

SDMMC0_D2 |

SDMMC0_D2/ARMJTAG_TCK/UART5_CTSn_M0/GPIO1_D7_u |

Porta dati SDMC0 |

3,3 V |

I/O SU

|

|

8 |

SDMMC0_D1 |

SDMMC0_D1/UART2_RX_M1/UART6_RX_M1/PWM9_M1/GPIO1_D6_u |

Porta dati SDMC0 |

3,3 V |

I/O SU

|

|

9 |

SDMMC0_D0 |

SDMMC0_D0/UART2_TX_M1/UART6_TX_M1/PWM8_M1/GPIO1_D5_u |

Porta dati SDMC0 |

3,3 V |

I/O SU

|

|

10 |

SDMMC0_CMD |

SDMMC0_CMD/PWM10_M1/UART5_RX_M0/CAN0_TX_M1/GPIO2_A1_u |

Uscita del comando SDMC0 |

3,3 V |

I/O SU

|

|

11 |

SDMMC0_CLK |

SDMMC0_CLK/TEST_CLKOUT/UART5_TX_M0/CAN0_RX_M1/GPIO2_A2_d |

Uscita orologio SDMC0

|

3,3 V |

I/O GIÙ |

|

12 |

RESETN |

NPOR_U |

Ripristina il rilevamento del segnale |

3,3 V |

- |

|

13 |

RK809_PWRON |

Accensione |

Ingresso segnale di accensione, tasto di accensione connessione esterna, attivo basso |

|

- |

|

14 |

RECUPERO |

SARADC_VIN0 |

Input da tastiera AD |

1,8 V |

- |

|

15 |

EXT_IT |

EXT_IT |

Abilitazione alimentazione PMIC |

|

- |

|

16 |

HPR_OUT |

HPR_OUT |

Cuffie subito fuori |

3,3 V |

- |

|

17 |

HPL_OUT |

HPL_OUT |

Cuffie lasciate fuori |

3,3 V |

- |

|

18 |

SPKP_OUT |

SPKP_OUT |

Parla |

5 V/0,6 W |

- |

|

19 |

SPKN_OUT |

SPKN_OUT |

Parla- |

5 V/0,6 W |

- |

|

20 |

MIC1_INN |

MIC1_INN/MIC_R |

MIC1_INN |

3,3 V |

- |

|

21 |

MIC1_ING |

MIC1_INP/MIC_L |

MIC1_ING |

3,3 V |

- |

|

22 |

HP_DET_L_GPIO3_C2 |

LCDC_VSYNC/VOP_BT1120_D14/SPI1_MISO_M1/UART5_TX_M1/I2S1_SDO3_M2/GPIO3_C2_d |

Rilevamento cuffie |

3,3 V |

I/O GIÙ |

|

23 |

SPK_CTL_H_GPIO3_C3 |

LCDC_DEN/VOP_BT1120_D15/SPI1_CLK_M1/UART5_RX_M1/I2S1_SCLK_RX_M2/GPIO3_C3_d |

|

3,3 V |

I/O GIÙ |

|

24 |

VCC3V3_SD |

Alimentazione da 3,3 V |

Tensione di uscita 3,3 V per scheda SD, corrente di uscita nominale 2 A |

|

- |

|

25 |

VCC_3V3 |

Alimentazione da 3,3 V |

Tensione di uscita 3,3 V, corrente di uscita nominale 2 A |

|

- |

|

26 |

VCC_1V8 |

Alimentazione da 1,8 V |

Tensione di uscita 1,8 V, corrente di uscita nominale 2,5 A |

|

- |

|

27 |

PDM_SDI1_M0_ADC |

I2S1_SDO3_M0/I2S1_SDI1_M0/PDM_SDI1_M0/PCIE20_PERSTn_M2/GPIO1_B2_d |

PDM_SDI1_M0_ADC |

3,3 V |

IO GIÙ |

|

28 |

PDM_SDI2_M0_ADC |

I2S1_SDO2_M0/I2S1_SDI2_M0/PDM_SDI2_M0/PCIE20_WAKEn_M2/ACODEC_ADC_SYNC/GPIO1_B1_d |

PDM_SDI2_M0_ADC |

3,3 V |

IO GIÙ |

|

29 |

PDM_SDI3_M0_ADC |

I2S1_SDO1_M0/I2S1_SDI3_M0/PDM_SDI3_M0/PCIE20_CLKREQn_M2/ACODEC_DAC_DATAR/GPIO1_B0_d |

PDM_SDI3_M0_ADC |

3,3 V |

IO GIÙ |

|

30 |

PDM_CLK1_M0_ADC |

I2S1_SCLK_RX_M0/UART4_RX_M0/PDM_CLK1_M0/SPDIF_TX_M0/GPIO1_A4_d |

PDM_CLK1_M0_ADC |

3,3 V |

IO GIÙ |

|

31 |

GMAC0_TXD0 |

GMAC0_TXD0/UART1_RX_M0/GPIO2_B3_u |

GMAC0 trasmette dati |

1,8 V |

I/O SU |

|

32 |

GMAC0_TXD1 |

GMAC0_TXD1/UART1_TX_M0/GPIO2_B4_u |

GMAC0 trasmette dati |

1,8 V |

I/O SU |

|

33 |

GMAC0_TXD2 |

SDMMC1_D3/GMAC0_TXD2/UART7_TX_M0/GPIO2_A6_u |

GMAC0 trasmette dati |

1,8 V |

I/O SU |

|

34 |

GMAC0_TXD3 |

SDMMC1_CMD/GMAC0_TXD3/UART9_RX_M0/GPIO2_A7_u |

GMAC0 trasmette dati |

1,8 V |

I/O SU |

|

35 |

GMAC0_TXIT |

GMAC0_TXEN/UART1_RTSn_M0/SPI1_CLK_M0/GPIO2_B5_u |

abilitazione trasmissione GMAC0 |

1,8 V |

I/O SU |

|

36 |

GMAC0_TXCLK |

SDMMC1_CLK/GMAC0_TXCLK/UART9_TX_M0/GPIO2_B0_d |

Orologio di trasmissione GMAC0 |

1,8 V |

I/O GIÙ |

|

37 |

GMAC0_RXD0 |

GMAC0_RXD0/UART1_CTSn_M0/SPI1_MISO_M0/GPIO2_B6_u |

GMAC0 riceve dati |

1.8 v |

I/O SU |

|

38 |

GMAC0_RXD1 |

I2S2_SCLK_RX_M0/GMAC0_RXD1/UART6_RTSn_M0/SPI1_MOSI_M0/GPIO2_B7_d |

GMAC0 riceve dati |

1,8 V |

I/O GIÙ |

|

39 |

GMAC0_RXD2 |

SDMMC1_D0/GMAC0_RXD2/UART6_RX_M0/GPIO2_A3_u |

GMAC0 riceve dati |

1.8 v |

I/O SU |

|

40 |

GMAC0_RXD3 |

SDMMC1_D1/GMAC0_RXD3/UART6_TX_M0/GPIO2_A4_u |

GMAC0 riceve dati |

1,8 V |

I/O SU |

|

41 |

GMAC0_RXDV_CRS |

I2S2_LRCK_RX_M0/GMAC0_RXDV_CRS/UART6_CTSn_M0/SPI1_CS0_M0/GPIO2_C0_d |

GMAC0 Segnale RX dati validi |

1,8 V |

I/O GIÙ |

|

42 |

GMAC0_RXCLK |

SDMMC1_D2/GMAC0_RXCLK/UART7_RX_M0/GPIO2_A5_u |

GMAC0 riceve l'orologio |

1,8 V |

I/O SU |

|

43 |

ETH0_REFCLKO_25M |

I2S2_MCLK_M0/ETH0_REFCLKO_25M/UART7_RTSn_M0/SPI2_CLK_M0/GPIO2_C1_d |

ETH0_REF CLOCK OUTPUT_25 MHz CPU a PHY, NC predefinito |

1,8 V |

I/O GIÙ |

|

44 |

GMAC0_MCLKINOUT |

I2S2_SCLK_TX_M0/GMAC0_MCLKINOUT/UART7_CTSn_M0/SPI2_MISO_M0/GPIO2_C2_d |

Orologio esterno GMAC0 |

1,8 V |

I/O GIÙ |

|

45 |

GMAC0_MDC |

I2S2_LRCK_TX_M0/GMAC0_MDC/UART9_RTSn_M0/SPI2_MOSI_M0/GPIO2_C3_d |

Orologio di gestione MAC0 |

1,8 V |

I/O GIÙ |

|

46 |

GMAC0_MDIO |

I2S2_SDO_M0/GMAC0_MDIO/UART9_CTSn_M0/SPI2_CS0_M0/GPIO2_C4_d |

Comando e dati di gestione MAC0 |

1,8 V |

I/O GIÙ |

|

47 |

GMAC0_RSTN_GPIO3_B7 |

LCDC_D21/VOP_BT1120_D12/GMAC1_TXD1_M0/I2C3_SDA_M1/PWM11_IR_M0/GPIO3_B6_d |

|

3,3 V |

IO GIÙ |

|

48 |

GMAC0_INT_PMEB_GPIO3_C0 |

LCDC_HSYNC/VOP_BT1120_D13/SPI1_MOSI_M1/PCIE20_PERSTn_M1/I2S1_SDO2_M2/GPIO3_C1_d |

|

3,3 V |

I/O GIÙ |

|

49 |

RTCTC_INT_L_GPIO0_D3 |

GPIO0_D3_d |

RTC_IC_INT, attivo basso |

1,8 V |

I/O GIÙ |

|

50 |

I2C5_SDA_M0 |

LCDC_D19/VOP_BT1120_D10/GMAC1_RXER_M0/I2C5_SDA_M0/PDM_SDI1_M2/GPIO3_B4_d |

Porta seriale I2C 5 |

3,3 V |

I/O GIÙ |

|

51 |

I2C5_SCL_M0 |

LCDC_D18/VOP_BT1120_D9/GMAC1_RXDV_CRS_M0/I2C5_SCL_M0/PDM_SDI0_M2/GPIO3_B3_d |

Porta seriale I2C 5 |

3,3 V |

I/O GIÙ |

|

52 |

PWM3_IR |

PWM3_IR/EDP_HPDIN_M1/PCIE30X1_WAKEn_M0/MCU_JTAG_TMS/GPIO0_C2_d |

|

3,3 V |

I/O GIÙ |

|

53 |

CAN1_TX_M1 |

PWM15_IR_M1/SPI3_MOSI_M1/CAN1_TX_M1/PCIE30X2_WAKEn_M2/I2S3_SCLK_M1/GPIO4_C3_d |

Trasmissione dati CAN |

3,3 V |

I/O GIÙ |

|

54 |

CAN1_RX_M1 |

PWM14_M1/SPI3_CLK_M1/CAN1_RX_M1/PCIE30X2_CLKREQn_M2/I2S3_MCLK_M1/GPIO4_C2_d |

CAN ricezione dati |

3,3 V |

I/O GIÙ |

|

55 |

UART2_RX_M0_DEBUG |

UART2_RX_M0/GPIO0_D0_u |

Porta seriale UART |

3,3 V |

I/O SU |

|

56 |

UART2_TX_M0_DEBUG |

UART2_TX_M0/GPIO0_D1_u |

Trasmissione dei dati della porta seriale UART per il debug |

3,3 V |

I/O SU |

|

57 |

UART3_RX_M1 |

LCDC_D23/PWM13_M0/GMAC1_MCLKINOUT_M0/UART3_RX_M1/PDM_SDI3_M2/GPIO3_C0_d |

Ricezione dati della porta seriale UART |

3,3 V |

I/O GIÙ |

|

58 |

UART3_TX_M1 |

LCDC_D22/PWM12_M0/GMAC1_TXEN_M0/UART3_TX_M1/PDM_SDI2_M2/GPIO3_B7_d |

Trasmissione dati della porta seriale UART |

3,3 V |

I/O GIÙ |

|

59 |

UART4_TX_M1 |

LCDC_D17/VOP_BT1120_D8/GMAC1_RXD1_M0/UART4_TX_M1/PWM9_M0/GPIO3_B2_d |

Trasmissione dati della porta seriale UART |

3,3 V |

I/O GIÙ |

|

60 |

UART4_RX_M1 |

LCDC_D16/VOP_BT1120_D7/GMAC1_RXD0_M0/UART4_RX_M1/PWM8_M0/GPIO3_B1_d |

Ricezione dati della porta seriale UART |

3,3 V |

I/O GIÙ |

|

61 |

UART9_RX_M1 |

PWM13_M1/SPI3_CS0_M1/SATA0_ACT_LED/UART9_RX_M1/I2S3_SDI_M1/GPIO4_C6_d |

Ricezione dati della porta seriale UART |

3,3 V |

I/O GIÙ |

|

62 |

UART9_TX_M1 |

PWM12_M1/SPI3_MISO_M1/SATA1_ACT_LED/UART9_TX_M1/I2S3_SDO_M1/GPIO4_C5_d |

Trasmissione dati della porta seriale UART |

3,3 V |

I/O GIÙ |

|

63 |

UART7_RX_M1 |

PWM15_IR_M0/SPDIF_TX_M1/GMAC1_MDIO_M0/UART7_RX_M1/I2S1_LRCK_RX_M2/GPIO3_C5_d |

Ricezione dati della porta seriale UART |

3,3 V |

I/O GIÙ |

|

64 |

UART7_TX_M1 |

PWM14_M0/VOP_PWM_M1/GMAC1_MDC_M0/UART7_TX_M1/PDM_CLK1_M2/GPIO3_C4_d |

Trasmissione dati della porta seriale UART |

3,3 V |

I/O GIÙ |

|

65 |

RS485_DIR_GPIO3_B5 |

LCDC_D20/VOP_BT1120_D11/GMAC1_TXD0_M0/I2C3_SCL_M1/PWM10_M0/GPIO3_B5_d |

Direzione dati RS485 |

3,3 V |

I/O GIÙ |

|

66 |

DVP_PWREN0_H_GPIO0_B0 |

CLK32K_IN/CLK32K_OUT0/PCIE30X2_BUTTONRSTn/GPIO0_B0_u |

|

3,3 V |

I/O SU |

|

67 |

WIFI_PWREN_L_GPIO0_C1 |

PWM2_M0/NPUAVS/UART0_TX/MCU_JTAG_TDI/GPIO0_C1_d |

|

3,3 V |

I/O GIÙ |

|

68 |

I2S3_SDI_M0 |

LCDC_D13/VOP_BT1120_CLK/GMAC1_TXCLK_M0/I2S3_SDI_M0/SDMMC2_CLK_M1/GPIO3_A6_d |

I2S3_SDI |

3,3 V |

I/O GIÙ |

|

69 |

I2S3_SDO_M0 |

LCDC_D12/VOP_BT1120_D4/GMAC1_RXD3_M0/I2S3_SDO_M0/SDMMC2_CMD_M1/GPIO3_A5_d |

I2S3_SDO |

3,3 V |

I/O GIÙ |

|

70 |

I2S3_LRCK_M0 |

LCDC_D11/VOP_BT1120_D3/GMAC1_RXD2_M0/I2S3_LRCK_M0/SDMMC2_D3_M1/GPIO3_A4_d |

I2S3_LRCK |

3,3 V |

I/O GIÙ |

|

71 |

I2S3_SCLK_M0 |

LCDC_D10/VOP_BT1120_D2/GMAC1_TXD3_M0/I2S3_SCLK_M0/SDMMC2_D2_M1/GPIO3_A3_d |

I2S3_SCLK |

3,3 V |

I/O GIÙ |

|

72 |

HOST_WAKE_BT_H_GPIO3_A2 |

LCDC_D9/VOP_BT1120_D1/GMAC1_TXD2_M0/I2S3_MCLK_M0/SDMMC2_D1_M1/GPIO3_A2_d |

HOST_WAKE_BT |

3,3 V |

I/O GIÙ |

|

73 |

BT_WAKE_HOST_H_GPIO3_A1 |

LCDC_D8/VOP_BT1120_D0/SPI1_CS0_M1/PCIE30X1_PERSTn_M1/SDMMC2_D0_M1/GPIO3_A1_d |

BT_WAKE_HOST |

3,3 V |

I/O GIÙ |

|

74 |

BT_REG_ON_H_GPIO3_A0 |

LCDC_CLK/VOP_BT656_CLK_M0/SPI2_CLK_M1/UART8_RX_M1/I2S1_SDO1_M2/GPIO3_A0_d |

Abilitazione alimentazione modulo Bluetooth |

3,3 V |

I/O GIÙ |

|

75 |

UART8_RX_M0 |

CLK32K_OUT1/UART8_RX_M0/SPI1_CS1_M0/GPIO2_C6_d |

Ricezione dati della porta seriale UART |

1,8 V |

I/O GIÙ |

|

76 |

UART8_TX_M0 |

I2S2_SDI_M0/GMAC0_RXER/UART8_TX_M0/SPI2_CS1_M0/GPIO2_C5_d |

Trasmissione dati della porta seriale UART |

1,8 V |

I/O GIÙ |

|

77 |

UART8_CTSN_M0 |

SDMMC1_DET/I2C4_SCL_M1/UART8_CTSn_M0/CAN2_TX_M1/GPIO2_B2_u |

UART8_CTSn_M0 |

1,8 V |

I/O GIÙ |

|

78 |

UART8_RTSN_M0 |

SDMMC1_PWREN/I2C4_SDA_M1/UART8_RTSn_M0/CAN2_RX_M1/GPIO2_B1_d |

UART8_RTSn_M0 |

1,8 V |

I/O GIÙ |

|

79 |

WIFI_REG_ON_H_GPIO3_D5 |

CIF_D7/EBC_SDDO7/SDMMC2_PWREN_M0/I2S1_SDI3_M1/VOP_BT656_D7_M1/GPIO3_D5_d |

WIFI_REG abilitato |

1,8 V |

I/O GIÙ |

|

80 |

WIFI_WAKE_HOST_H_GPIO3_D4 |

CIF_D6/EBC_SDDO6/SDMMC2_DET_M0/I2S1_SDI2_M1/VOP_BT656_D6_M1/GPIO3_D4_d |

Host di sveglia WIFI |

1,8 V |

I/O GIÙ |

|

81 |

SDMMC2_CLK_M0 |

CIF_D5/EBC_SDDO5/SDMMC2_CLK_M0/I2S1_SDI1_M1/VOP_BT656_D5_M1/GPIO3_D3_d |

Orologio SDMMC2 |

1,8 V |

I/O GIÙ |

|

82 |

SDMMC2_CMD_M0 |

CIF_D4/EBC_SDDO4/SDMMC2_CMD_M0/I2S1_SDI0_M1/VOP_BT656_D4_M1/GPIO3_D2_d |

Comando SDMMC2 |

1,8 V |

I/O GIÙ |

|

83 |

SDMMC2_D3_M0 |

CIF_D3/EBC_SDDO3/SDMMC2_D3_M0/I2S1_SDO0_M1/VOP_BT656_D3_M1/GPIO3_D1_d |

Dati SDMC2 |

1,8 V |

I/O GIÙ |

|

84 |

SDMMC2_D2_M0 |

CIF_D2/EBC_SDDO2/SDMMC2_D2_M0/I2S1_LRCK_TX_M1/VOP_BT656_D2_M1/GPIO3_D0_d |

Dati SDMC2 |

1,8 V |

I/O GIÙ |

|

85 |

SDMMC2_D1_M0 |

CIF_D1/EBC_SDDO1/SDMMC2_D1_M0/I2S1_SCLK_TX_M1/VOP_BT656_D1_M1/GPIO3_C7_d |

Dati SDMC2 |

1,8 V |

I/O GIÙ |

|

86 |

SDMMC2_D0_M0 |

CIF_D0/EBC_SDDO0/SDMMC2_D0_M0/I2S1_MCLK_M1/VOP_BT656_D0_M1/GPIO3_C6_d |

Dati SDMC2 |

1,8 V |

I/O GIÙ |

|

87 |

GMAC1_INT/PMEB_GPIO3_A7 |

LCDC_D14/VOP_BT1120_D5/GMAC1_RXCLK_M0/SDMMC2_DET_M1/GPIO3_A7_d |

|

3,3 V |

I/O GIÙ |

|

88 |

GMAC1_RSTN_GPIO3_B0 |

LCDC_D15/VOP_BT1120_D6/ETH1_REFCLKO_25M_M0/SDMMC2_PWREN_M1/GPIO3_B0_d |

|

3,3 V |

I/O GIÙ |

|

89 |

GMAC1_MDIO_M1 |

IF_VSYNC/EBC_SDOE/GMAC1_MDIO_M1/I2S2_SCLK_TX_M1/GPIO4_B7_d |

Comando e dati di gestione GMAC1 |

1,8 V |

I/O GIÙ |

|

90 |

GMAC1_MDC_M1 |

CIF_HREF/EBC_SDLE/GMAC1_MDC_M1/UART1_RTSn_M1/I2S2_MCLK_M1/GPIO4_B6_d |

Orologio di gestione GMAC1 |

1,8 V |

I/O GIÙ |

|

91 |

GMAC1_MCLKINOUT_M1 |

CIF_CLKIN/EBC_SDCLK/GMAC1_MCLKINOUT_M1/UART1_CTSn_M1/I2S2_SCLK_RX_M1/GPIO4_C1_d |

Orologio esterno GMAC1 |

1,8 V |

I/O GIÙ |

|

92 |

ETH1_REFCLKO_25M_M1 |

I2C4_SCL_M0/EBC_GDOE/ETH1_REFCLKO_25M_M1/SPI3_CLK_M0/I2S2_SDO_M1/GPIO4_B3_d |

ETH1 Uscita orologio |

1,8 V |

I/O GIÙ |

|

93 |

GMAC1_RXCLK_M1 |

CIF_D13/EBC_SDDO13/GMAC1_RXCLK_M1/UART7_RX_M2/PDM_SDI3_M1/GPIO4_A3_d |

Orologio di ricezione GMAC1 |

1,8 V |

I/O GIÙ |

|

94 |

GMAC1_RXDV_CRS_M1 |

ISP_PRELIGHT_TRIG/EBC_SDCE3/GMAC1_RXDV_CRS_M1/I2S1_SDO2_M1/GPIO4_B1_d |

GMAC1 Segnale RX dati validi |

1,8 V |

I/O GIÙ |

|

95 |

GMAC1_RXD3_M1 |

CIF_D12/EBC_SDDO12/GMAC1_RXD3_M1/UART7_TX_M2/PDM_SDI2_M1/GPIO4_A2_d |

GMAC1 riceve dati |

1,8 V |

I/O GIÙ |

|

96 |

GMAC1_RXD2_M1 |

CIF_D11/EBC_SDDO11/GMAC1_RXD2_M1/PDM_SDI1_M1/GPIO4_A1_d |

GMAC1 riceve dati |

1,8 V |

I/O GIÙ |

|

97 |

GMAC1_RXD1_M1 |

CAM_CLKOUT1/EBC_SDCE2/GMAC1_RXD1_M1/SPI3_MISO_M0/I2S1_SDO1_M1/GPIO4_B0_d |

GMAC1 riceve dati |

1,8 V |

I/O GIÙ |

|

98 |

GMAC1_RXD0_M1 |

CAM_CLKOUT0/EBC_SDCE1/GMAC1_RXD0_M1/SPI3_CS1_M0/I2S1_LRCK_RX_M1/GPIO4_A7_d |

GMAC1 riceve dati |

1,8 V |

I/O GIÙ |

|

99 |

GMAC1_TXCLK_M1 |

CIF_D10/EBC_SDDO10/GMAC1_TXCLK_M1/PDM_CLK1_M1/GPIO4_A0_d |

Orologio di trasmissione GMAC1 |

1,8 V |

I/O GIÙ |

|

100 |

GMAC1_TXIT_M1 |

ISP_FLASHTRIGOUT/EBC_SDCE0/GMAC1_TXEN_M1/SPI3_CS0_M0/I2S1_SCLK_RX_M1/GPIO4_A6_d |

abilitazione trasmissione GMAC1 |

1,8 V |

I/O GIÙ |

|

101 |

GMAC1_TXD3_M1 |

CIF_D9/EBC_SDDO9/GMAC1_TXD3_M1/UART1_RX_M1/PDM_SDI0_M1/GPIO3_D7_d |

GMAC1 trasmette dati |

1,8 V |

I/O GIÙ |

|

102 |

GMAC1_TXD2_M1 |

CIF_D8/EBC_SDDO8/GMAC1_TXD2_M1/UART1_TX_M1/PDM_CLK0_M1/GPIO3_D6_d |

GMAC1 trasmette dati |

1,8 V |

I/O GIÙ |

|

103 |

GMAC1_TXD1_M1 |

CIF_D15/EBC_SDDO15/GMAC1_TXD1_M1/UART9_RX_M2/I2S2_LRCK_RX_M1/GPIO4_A5_d |

GMAC1 trasmette dati |

1,8 V |

I/O GIÙ |

|

104 |

GMAC1_TXD0_M1 |

CIF_D14/EBC_SDDO14/GMAC1_TXD0_M1/UART9_TX_M2/I2S2_LRCK_TX_M1/GPIO4_A4_d |

GMAC1 trasmette dati |

1,8 V |

I/O GIÙ |

|

105 |

TP_RST_L_GPIO0_B6 |

I2C2_SDA_M0/SPI0_MOSI_M0/PCIE20_PERSTn_M0/PWM2_M1/GPIO0_B6_u |

Ripristino del pannello tattile |

3,3 V |

I/O SU

|

|

106 |

TP_INT_L_GPIO0_B5 |

I2C2_SCL_M0/SPI0_CLK_M0/PCIE20_WAKEn_M0/PWM1_M1/GPIO0_B5_u |

Input di dati di interruzione del touchpanel |

3,3 V |

I/O SU |

|

107 |

I2C1_SDA_TP |

I2C1_SDA/CAN0_RX_M0/PCIE20_BUTTONRSTn/MCU_JTAG_TCK/GPIO0_B4_u |

Porta seriale I2C 1 |

3,3 V |

I/O SU |

|

108 |

I2C1_SCL_TP |

I2C1_SCL/CAN0_TX_M0/PCIE30X1_BUTTONRSTn/MCU_JTAG_TDO/GPIO0_B3_u |

Porta seriale I2C 1 |

3,3 V |

I/O SU |

|

109 |

I2C3_SCL_M0 |

I2C3_SCL_M0/UART3_TX_M0/CAN1_TX_M0/AUDIOPWM_LOUT_N/ACODEC_ADC_CLK/GPIO1_A1_u |

Porta seriale I2C 3 |

3,3 V |

I/O SU |

|

110 |

I2C3_SDA_M0 |

I2C3_SDA_M0/UART3_RX_M0/CAN1_RX_M0/AUDIOPWM_LOUT_P/ACODEC_ADC_DATA/GPIO1_A0_u |

Porta seriale I2C 3 |

3,3 V |

I/O SU |

|

111 |

I2C2_SCL_M1 |

I2C2_SCL_M1/EBC_SDSHR/CAN2_TX_M0/I2S1_SDO3_M1/GPIO4_B5_d |

Porta seriale I2C 2 |

1,8 V |

I/O GIÙ |

|

112 |

I2C2_SDA_M1 |

I2C2_SDA_M1/EBC_GDSP/CAN2_RX_M0/ISP_FLASH_TRIGIN/VOP_BT656_CLK_M1/GPIO4_B4_d |

Porta seriale I2C 2 |

1,8 V |

I/O GIÙ |

|

113 |

MIPI_CAM1_PDN_L_GPIO3_D3 |

LCDC_D1/VOP_BT656_D1_M0/SPI0_MOSI_M1/PCIE20_WAKEn_M1/I2S1_SCLK_TX_M2/GPIO2_D1_d |

Spegnere la telecamera1 |

3,3 V |

I/O GIÙ |

|

114 |

MIPI_CAM1_RST_L_GPIO3_D2 |

LCDC_D0/VOP_BT656_D0_M0/SPI0_MISO_M1/PCIE20_CLKREQn_M1/I2S1_MCLK_M2/GPIO2_D0_d |

Ripristino telecamera1 |

3,3 V |

I/O GIÙ |

|

115 |

MIPI_CAM0_RST_L_GPIO3_D4 |

LCDC_D2/VOP_BT656_D2_M0/SPI0_CS0_M1/PCIE30X1_CLKREQn_M1/I2S1_LRCK_TX_M2/GPIO2_D2_d |

Ripristino telecamera0 |

3,3 V |

I/O GIÙ |

|

116 |

MIPI_CAM0_PDN_L_GPIO3_D5 |

LCDC_D3/VOP_BT656_D3_M0/SPI0_CLK_M1/PCIE30X1_WAKEn_M1/I2S1_SDI0_M2/GPIO2_D3_d |

Spegnere la fotocamera0 |

3,3 V |

I/O GIÙ |

|

117 |

USB2_HOST2_DM |

USB2_HOST2_DM |

USB2_HOST2_DM |

3,3 V |

- |

|

118 |

USB2_HOST2_DP |

USB2_HOST2_DP |

USB2_HOST2_DP |

3,3 V |

- |

|

119 |

USB2_HOST3_DM |

USB2_HOST3_DM |

USB2_HOST3_DM |

3,3 V |

- |

|

120 |

USB2_HOST3_DP |

USB2_HOST3_DP |

USB2_HOST3_DP |

3,3 V |

- |

|

121 |

REFCLK_OUT |

REFCLK_OUT/GPIO0_A0_d |

Uscita orologio per fotocamera |

3,3 V |

I/O GIÙ |

|

122 |

CIF_CLKOUT |

CIF_CLKOUT/EBC_GDCLK/PWM11_IR_M1/GPIO4_C0_d |

Orologio CIF scaduto |

1,8 V |

I/O GIÙ |

|

123 |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

1,8 V |

- |

|

124 |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

1,8 V |

- |

|

125 |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

1,8 V |

- |

|

126 |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

1,8 V |

- |

|

127 |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

1,8 V |

- |

|

128 |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

1,8 V |

- |

|

129 |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

1,8 V |

- |

|

130 |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

1,8 V |

- |

|

131 |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

1,8 V |

- |

|

132 |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

1,8 V |

- |

|

133 |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

1,8 V |

- |

|

134 |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

1,8 V |

- |

|

135 |

LCD1_PWREN_H_GPIO0_C5 |

PWM6/SPI0_MISO_M0/PCIE30X2_WAKEn_M0/GPIO0_C5_d |

Abilitazione alimentazione LCD |

3,3 V |

I/O GIÙ |

|

136 |

LCD1_BL_PWM5 |

PWM5/SPI0_CS1_M0/UART0_RTSn/GPIO0_C4_d |

LCD retroilluminato PWM |

3,3 V |

I/O GIÙ |

|

137 |

LCD1_BL_PWM4 |

PWM4/VOP_PWM_M0/PCIE30X1_PERSTn_M0/MCU_JTAG_TRSTn/GPIO0_C3_d |

LCD retroilluminato PWM |

3,3 V |

I/O GIÙ |

|

138 |

LCD0_PWREN_H_GPIO0_C7 |

HDMITX_CEC_M1/PWM0_M1/UART0_CTSn/GPIO0_C7_d |

Abilitazione alimentazione LCD |

3,3 V |

I/O GIÙ |

|

139 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

1,8 V |

- |

|

140 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

1,8 V |

- |

|

141 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

1,8 V |

- |

|

142 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

1,8 V |

- |

|

143 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

1,8 V |

- |

|

144 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

1,8 V |

- |

|

145 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

1,8 V |

- |

|

146 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

1,8 V |

- |

|

147 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

1,8 V |

- |

|

148 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

1,8 V |

- |

|

149 |

HDMI_TXCLKN_PORT |

HDMI_TX_CLKN |

HDMI_TX2CLKN_PORT e resistenza serie 2.2R |

1,8 V |

- |

|

150 |

HDMI_TXCLKP_PORT |

HDMI_TX_CLKP |

HDMI_TXCLKP_PORT e resistenza serie 2.2R |

1,8 V |

- |

|

151 |

HDMI_TX0N_PORT |

HDMI_TX_D0N |

HDMI_TX0N_PORT e resistenza serie 2.2R |

1,8 V |

- |

|

152 |

HDMI_TX0P_PORT |

HDMI_TX_D0P |

HDMI_TX0P_PORT e resistenza serie 2.2R |

1,8 V |

- |

|

153 |

HDMI_TX1N_PORT |

HDMI_TX_D1N |

HDMI_TX1N_PORT e resistenza serie 2.2R |

1,8 V |

- |

|

154 |

HDMI_TX1P_PORT |

HDMI_TX_D1P |

HDMI_TX1P_PORT e resistenza serie 2.2R |

1,8 V |

- |

|

155 |

HDMI_TX2N_PORT |

HDMI_TX_D2N |

HDMI_TX2N_PORT e resistenza serie 2.2R |

1,8 V |

- |

|

156 |

HDMI_TX2P_PORT |

HDMI_TX_D2P |

HDMI_TX2P_PORT e resistenza serie 2.2R |

1,8 V |

- |

|

157 |

HDMITX_SCL |

HDMITX_SCL/I2C5_SCL_M1/GPIO4_C7_u |

Porta seriale I2C per HDMI |

3,3 V |

I/O SU |

|

158 |

HDMITC_SDA |

HDMITX_SDA/I2C5_SDA_M1/GPIO4_D0_u |

Porta seriale I2C per HDMI |

3,3 V |

I/O SU |

|

159 |

HDMITX_CEC_M0 |

HDMITX_CEC_M0/SPI3_CS1_M1/GPIO4_D1_u |

HDMITX_CEC |

3,3 V |

I/O SU |

|

160 |

HDMI_TX_HPDIN |

HDMI_TX_HPDIN |

presa calda HDMI_TX |

1,8 V |

- |

|

161 |

PCIE30X2_CLKREQN_M1 |

LCDC_D4/VOP_BT656_D4_M0/SPI2_CS1_M1/PCIE30X2_CLKREQn_M1/I2S1_SDI1_M2/GPIO2_D4_d |

PCIE30X2_CLKREQn |

3.3 |

I/O GIÙ |

|

162 |

PCIE30X2_WAKEN_M1 |

LCDC_D5/VOP_BT656_D5_M0/SPI2_CS0_M1/PCIE30X2_WAKEn_M1/I2S1_SDI2_M2/GPIO2_D5_d |

PCIE30X2_WAKEn |

3,3 V |

I/O GIÙ |

|

163 |

PCIE30X2_PERSTN_M1 |

LCDC_D6/VOP_BT656_D6_M0/SPI2_MOSI_M1/PCIE30X2_PERSTn_M1/I2S1_SDI3_M2/GPIO2_D6_d |

Ripristino PCIE30X2 |

3,3 V |

I/O GIÙ |

|

164 |

PCIE30X2_PRSNT_L_GPIO2_D7 |

LCDC_D7/VOP_BT656_D7_M0/SPI2_MISO_M1/UART8_TX_M1/I2S1_SDO0_M2/GPIO2_D7_d |

Host di riattivazione PCIE30X2 |

3,3 V |

I/O GIÙ |

|

165 |

PCIE_PWREN_H_GPIO0_D4 |

GPIO0_D4_d |

abilitazione alimentazione PCIE |

1,8 V |

I/O GIÙ |

|

166 |

PCIE30_RX1N |

PCIE30_RX1N |

PCIE30_RX1N |

1,8 V |

- |

|

167 |

PCIE30_RX1P |

PCIE30_RX1P |

PCIE30_RX1P |

1,8 V |

- |

|

168 |

PCIE30_RX0N |

PCIE30_RX0N |

PCIE30_RX0N |

1,8 V |

- |

|

169 |

PCIE30_RX0P |

PCIE30_RX0P |

PCIE30_RX0P |

1,8 V |

- |

|

170 |

PCIE30_TX1N |

PCIE30_TX1N |

PCIE30_TX1N |

1,8 V |

- |

|

171 |

PCIE30_TX1P |

PCIE30_TX1P |

PCIE30_TX1P |

1,8 V |

- |

|

172 |

PCIE30_TX0N |

PCIE30_TX0N |

PCIE30_TX0N |

1,8 V |

- |

|

173 |

PCIE30_TX0P |

PCIE30_TX0P |

PCIE30_TX0P |

1,8 V |

- |

|

174 |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

1,8 V |

- |

|

175 |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

1,8 V |

- |

|

176 |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

1,8 V |

- |

|

177 |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

1,8 V |

- |

|

178 |

SATA2_RXN |

PCIE20_RXN/SATA2_RXN/QSGMII_RXN_M1 |

SATA2_RXN |

1,8 V |

- |

|

179 |

SATA2_RXP |

PCIE20_RXP/SATA2_RXP/QSGMII_RXP_M1 |

SATA2_RXP |

1,8 V |

- |

|

180 |

SATA2_TXN |

PCIE20_TXN/SATA2_TXN/QSGMII_TXN_M1 |

SATA2_TXN |

1,8 V |

- |

|

181 |

SATA2_TXP |

PCIE20_TXP/SATA2_TXP/QSGMII_TXP_M1 |

SATA2_TXP |

1,8 V |

- |

|

182 |

SATA2_ACT_LED |

EDP_HPDIN_M0/SPDIF_TX_M2/SATA2_ACT_LED/PCIE30X2_PERSTn_M2/I2S3_LRCK_M1/GPIO4_C4_d |

SATA attivo indica |

3,3 V |

I/O GIÙ |

|

183 |

USB3_HOST1_SSTXP |

USB3_HOST1_SSTXP/SATA1_TXP/QSGMII_TXP_M0 |

USB3_HOST1_SSTXP |

1,8 V |

- |

|

184 |

USB3_HOST1_SSTXN |

USB3_HOST1_SSTXN/SATA1_TXN/QSGMII_TXN_M0 |

USB3_HOST1_SSTXN |

1,8 V |

- |

|

185 |

USB3_HOST1_SSRXP |

USB3_HOST1_SSRXP/SATA1_RXP/QSGMII_RXP_M0 |

USB3_HOST1_SSRXP |

1,8 V |

- |

|

186 |

USB3_HOST1_SSRXN |

USB3_HOST1_SSRXN/SATA1_RXN/QSGMII_RXN_M0 |

USB3_HOST1_SSRXN |

1,8 V |

- |

|

187 |

USB3_HOST1_DM |

USB3_HOST1_DM |

USB3_HOST1_DM |

3,3 V |

- |

|

188 |

USB3_HOST1_DP |

USB3_HOST1_DP |

USB3_HOST1_DP |

3,3 V |

- |

|

189 |

USB3_OTG0_SSTXP |

USB3_OTG0_SSTXP/SATA0_TXP |

USB3_OTG0_SSTXP |

1,8 V |

- |

|

190 |

USB3_OTG0_SSTXN |

USB3_OTG0_SSTXN/SATA0_TXN |

USB3_OTG0_SSTXN |

1,8 V |

- |

|

191 |

USB3_OTG0_SSRXP |

USB3_OTG0_SSRXP/SATA0_RXP |

USB3_OTG0_SSRXP |

1,8 V |

- |

|

192 |

USB3_OTG0_SSRXN |

USB3_OTG0_SSRXN/SATA0_RXN |

USB3_OTG0_SSRXN |

1,8 V |

- |

|

193 |

USB3_OTG0_DM |

USB3_OTG0_DM |

USB3_OTG0_DM |

3,3 V |

- |

|

194 |

USB3_OTG0_DP |

USB3_OTG0_DP |

USB3_OTG0_DP |

3,3 V |

- |

|

195 |

USB3_OTG0_ID |

USB3_OTG0_ID |

USB3_OTG0_ID |

3,3 V |

- |

|

196 |

USB3_OTG0_VBUSDET |

USB3_OTG0_VBUSDET |

Rilevamento USB3_OTG0_VBUS |

3,3 V |

- |

|

197 |

USB_HOST_PWREN_H_GPIO0_A6 |

GPU_PWREN/SATA_CP_POD/PCIE30X2_CLKREQn_M0/GPIO0_A6_d |

Abilitazione alimentazione host USB |

3,3 V |

I/O GIÙ |

|

198 |

USB_OTG_PWREN_H_GPIO0_A5 |

SDMMC0_PWREN/SATA_MP_SWITCH/PCIE20_CLKREQn_M0/GPIO0_A5_d |

Abilitazione alimentazione USB OTG |

3,3 V |

I/O GIÙ |

|

199 |

DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

1,8 V |

- |

|

200 |

DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

1,8 V |

- |

|

201 |

DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

1,8 V |

- |

|

202 |

DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

1.8 v |

- |

|

203 |

DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

1,8 V |

- |

|

204 |

DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

1,8 V |

- |

|

205 |

DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

1,8 V |

- |

|

206 |

DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

1,8 V |

- |

|

207 |

DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

1,8 V |

- |

|

208 |

DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

1,8 V |

- |

Capitolo 3. Consiglio di sviluppo

Misurare

La dimensione è 150 mm * 110 mm, 4 strati, spessore 1,6 mm.

Descrizione delle interfacce

|

Descrizione delle interfacce |

|

|

NO. |

Nome |

|

ã1ã |

Ingresso CC 12V/4 pin 2,54 mm Ingresso 12V |

|

ã2ã |

Slot per scheda SIM modulo 4G |

|

ã3ã |

Slot per schede TF |

|

ã4ã |

USB OTG |

|

ã5ã |

HOST USB 3.0 |

|

ã6ã |

Dati SATA |

|

ã7ã |

Uscita HDMI |

|

ã8ã |

LCD MIPI1 |

|

ã9ã |

MIPI LCD0 |

|

ã10ã |

Fotocamera MIPI |

|

ã11ã |

USB 2.0 * 3 |

|

ã12ã |

USB 2.0 Tipo A |

|

ã13ã |

WIFI/BT(AP6335) |

|

ã14ã |

RTC |

|

ã15ã |

ETH0 |

|

ã16ã |

ETH1 |

|

ã17ã |

Aggiorna chiave |

|

ã18ã |

Chiave di ripristino |

|

ã19ã |

Tasto d'accensione |

|

ã20ã |

Tasti (4 pin 2,0 mm) |

|

ã21ã |

PUÒ (3 pin 2,0 mm) |

|

ã22ã |

Uart TTL (4 pin 2,0 mm) |

|

ã23ã |

RS232 * 2 (4 pin 2,0 mm) |

|

ã24ã |

RS485 (4 pin 2,0 mm) |

|

ã25ã |

VENTOLA (2 pin 2,0 mm) |

|

ã26ã |

MICROFONO (2 pin 2,0 mm) |

|

ã27ã |

HP (2 pin 2,0 mm) |

|

ã28ã |

SPK (2 pin 2,0 mm) |

|

ã29ã |

Alimentazione in uscita (4 pin 2,0 mm) |

|

ã30ã |

Debug Uart (4 pin 2,0 mm) |

|

ã31ã |

GPIO(2*10pin 2,0mm) |

|

ã32ã |

Slot modulo 4G (porta PCIE) |

|

ã33ã |

RK3568 SOM |

La scheda utilizza un'alimentazione a 12 V CC, che si collega tramite un connettore di ingresso CC a 12 V o un connettore di ingresso a 4 pin da 2,54 mm a 12 V.

Dettagli di altre interfacce, potrebbero fare riferimento al diagramma schematico e al layout della scheda di sviluppo.

Capitolo 4. Progettazione hardware

Riferimento di progettazione

Prendi la scheda di sviluppo TC-RK3568 come piattaforma hardware, puoi fare riferimento a Power design, USB design, PCIE Port design, MIPI display design, Audio design, Ethernet design, Camera design e così via. Questi sono aperti ai clienti, possono fare riferimento al nostro design della scheda portante.

Capitolo 5. Progettazione del software

La piattaforma di sviluppo TC-RK3568 supporta Android11, Linux Buildroot, Ubuntu e Debian System OS, i codici sorgente sono aperti. È possibile leggere i riferimenti come il manuale utente del sistema Thinkcore TC-RK3568.